Top / MeRLの研究方法MeRLの研究方法

研究テーマの選定 †

研究室への配属が決まったら、研究テーマの選定と研究計画の作成をしてもらいます。学部4年生でも、新規に研究テーマを提案できる実力のある人は、どんどん提案して下さい。とくにやりたい具体的な研究テーマを持って、研究室に来たのでなければ、最初のうちは先輩や教員の研究を見聞きして、既存の研究プロジェクトの中から選んでもかまいません。

研究計画 †

研究テーマが決まったら、1年を通しての具体的な研究計画表を作成して、研究報告会で発表してもらいます。また、進学することが決まっている人は、大学院期間まで通して計画を作成してもかまいません。研究計画表といっても、プロジェクト管理に使用するガントチャートのような簡単なもので十分です。

研究室の生活 †

大抵の研究室で、原則として、他の優先用件がなければ、夏休みも含めて、毎日研究室に来ることになります(研究室にもよるかもしれませんが)。その目的は下記の2点です。

- 常に頭を発想モードにするための練習

- 発想に必要な情報共有と多次元のアンテナ形成

さあ、今から研究するぞ・・・といって研究できるものではないので、先ず、常にいろいろなことに興味を持って、見聞きしたことから課題を発見する姿勢を身につける必要があります。アイデアを出すのが苦手という学生が多いのですが、たぶん、自分の関心に沿った複数の課題を持っていないためです。アイデアを発想するためには、事前にいろいろな課題を発見して頭の隅に置いておく必要があります。さらに、ある程度訓練すると、研究室にいなくても、どこでも発想のトリガがかかるようになりますが、一人の頭から出てくる発想はたかが知れているので、他の人と互いに情報を共有して多次元のアンテナを形成する必要があります。これは研究室内だけではなく、いろいろな場所で行うべきことですが、知財保護やアイデアの流出防止の観点で、研究室内なら気楽だというだけのことです。課題の発見とアイデアの発想は、就職後も研究開発や経営に関わるかぎり一生続けることになります。仕事や新しいことを学ぶのが楽しくて仕方がない人と、そうでない人(こちらの方が多いかな?)の違いは、頭が発想モードになっているかどうかであり、この違いによって人生の目的や意義も根本から違ってきます。

研究室の行事 †

研究室に所属すると、研究活動に関する行事、親睦のための行事、健康のための行事など、いろいろな行事が待っています。

- 特許出願

- 学会発表/国際会議

- 展示会出展

- 論文発表(主に大学院生)

- 評価設備, 設計講習会

- 論文等の輪講

- 東京大学VDEC主催行事

- 共同研究ミーティング

- 卒業研究発表会/修士論文発表会/学位論文公聴会

- その他, レクリエーション行事や親睦行事

- 多くの行事がありますが、企画力や行動力のある学生がいないと実施できません。是非、先輩のノウハウを盗んで、楽しい研究生活を演出してください。

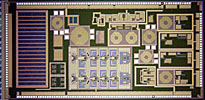

研究設備 †

MeRLでは、LSIや回路基板の製造はメーカに依頼するため、製造設備は持っていません。その代わりに、設計・シミュレーション環境、LSI設計、回路特性の測定に必要な機器はかなり充実しています。また、学生間の活発な討論が行われるような部屋配置などの配慮をしています。

- 学生部屋(2B724 + 2B734)

- 配属された学生は、学生部屋に机とPCを置き、普段はそこで研究を実施しています。半年に1回ぐらい席替えをします。

- ミーティング部屋(2B734)

- レーザカッタによる工作、プロジェクタ等を使った討論会ができます。オシロやマルチメータなどの汎用計測器もこちらにあります。

- はんだ部屋(2B736 + 2B724)

- ifDLの設備をお借りしています。ほとんどの工具が揃っており、回路のプリント基板実装がすぐにできます。簡単な基板作成や半田付けは、測定部屋でもできます。

- 測定部屋(2B724)

- 回路特性、高周波特性、光学特性などの計測を行うための精密計測器類、および計測器制御ソフトが揃っています。たいていの電子部品もここで揃います。

- VLSI評価試験室(VBL棟1階)

- VDEC北陸支部の共有設備です。ワイヤーボンダーなどの大型設備があります。

- VLSI設計CADサーバ

- エミュレータ(8000万ゲートクラス)や業界標準のCADツール環境が、VDEC北陸支部設備として用意されています。各自OCからからリモートで利用します。

- 東京大学システムデザイン研究センター(VDEC)

- 金沢大学にない設備については、東京大学の設備を利用することができます。半導体製造設備や評価設備が、ほとんど何でも揃っています。