# 目次

| は | じめ  | りに   |    |   |    |    |    |   |   | <br> | <br> | <br> | <br> | <br> |      | <br> | <br> | • | <br> | <br>• | <br> | <br> | <br>  | 3 |

|---|-----|------|----|---|----|----|----|---|---|------|------|------|------|------|------|------|------|---|------|-------|------|------|-------|---|

| 1 | . 相 | 既要   |    |   |    |    |    |   |   | <br> | <br> | <br> | <br> | <br> |      | <br> | <br> |   | <br> |       | <br> | <br> | <br>  | 4 |

| 2 | . 2 | Þ IP | の構 | 成 |    |    |    |   |   | <br> | <br> |      | <br> |      | <br> | <br> |      |   | <br> | <br>  | <br> | <br> | <br>  | 5 |

| 3 | . 2 | ķ IP | の使 | 用 | 方法 | 去  |    |   |   | <br> | <br> |      | <br> |      | <br> | <br> |      |   | <br> | <br>  | <br> | <br> | <br>  | 6 |

| 4 | . 2 | ķ IP | の性 | 能 | يط | 今後 | きの | 展 | 望 |      | <br> |      | <br> |      | <br> | <br> |      |   | <br> | <br>  | <br> | <br> | <br>  | 9 |

| 5 | . 🖠 | 多考文  | て献 |   |    |    |    |   |   | <br> |   | <br> |       | <br> | <br> | <br>1 | 0 |

## はじめに

本ドキュメントはMicrochipTechnology 社 PIC16F84 命令セット互換コントローラ IP に関する仕様書です.PIC16F84 に関する仕様・詳細な情報は,MicrochipTechnology 社のデータシートを参照してください.

## 1.概要

ここでは, MicrochipTechnology 社 PIC16F84 命令セット互換コントローラ IP (以下,本IP)の概要を以下に示します.

#### 1.1 本 IP の概要

- ・すべての命令は1ワード,命令数:35

- ・2 サイクルの分岐命令を除いて, すべて1 サイクル命令(1 サイクル = 4 x クロック周期)

- ・プログラムメモリ:最大8192×14(ワード)

- ・データ RAM(レジスタファイル): 最大464×8(バイト)

- ・ハードウエアスタック:8レベル

- ・直接,間接,相対の各アドレッシングモード

- ・割り込みソース

- ・外部 RB0 ピン

- ・TMRO タイマのオーバーフロー

- ・PORTB[7:4] ピン変化による割り込み

- ・I/O ピン数: 13(ピンごとに入出力設定可能)

- ・TMR0:8ビットタイマ プログラマブル8ビットプリスケーラー付き

- ・スリープモード(低消費電力モード)

#### 1.2 PIC16F84 との違い

- ・パワーオンリセット,パワーアップタイマ,オシレータスタートアップタイマ,ウォッチドッグタイマなどの機能は実装していません.ウォッチドッグタイマを実装していないので,CLRWDT 命令は NOP 命令と同じ動作をします.

- ・EEPROM 用のバスやレジスタは用意していません.

- ・プログラムメモリは最大で8192ワードまで搭載できます.

- ・レジスタファイルの量は自由に変更でき,Bank0から Bank3まで使えるようになっています.

## 2.本 IP の構成

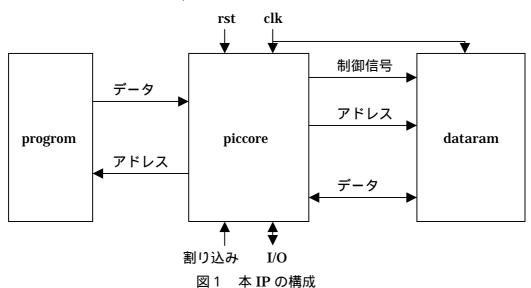

ここでは,本 IP の各モジュールの階層構造と入出力信号について述べます.

#### 2.1 各モジュールの階層構造

ogpic ... CPU コア + データ RAM + プログラム ROM のトップモジュール

- |---- piccore ... CPU コア , タイマ , 割り込み制御

- |---- dataram ... データ RAM(レジスタファイル)

- |---- progrom ... プログラム ROM(HEXtoVerilog.exe により作成します.3.3節で詳しく述べます)

#### 2.2 入出力信号

以下に本 IP の入出力を示します.

- 入力 ・clkin クロック入力端子

- ・mclr\_n リセット端子(low:リセット high:リセット解除)

- ・ponrst\_n リセット端子(low:リセット high:リセット解除) パワーオンリセット用の端子であるが,回路が実装されていないので 常に high にしてください.

- 出力 ・clkout 内部命令サイクルクロック(4×クロック周期)

- ・powerdown SLEEP 命令実行後に high になります

- ・startclkin 割り込み(外部 RBO, PORTB[7:4]端子変化), リセットにより high になります

- 入出力 · ra4~ra0 PORTA

- · rb7 ~ rb0 PORTB

### 3.本 IP の使用方法

ここでは,本IPの使用方法について述べます.基本的にはPIC16F84と同等の動作をしますので 詳細はMicrochipTechnology社のデータシートや各種参考書を参照してください.ここでは,本IPとPIC16F84とでの動作が異なる部分等について述べます.

#### 3.1 命令セット

- ・CLRWDT 命令:ウォッチドッグタイマを実装していないため, NOP 命令として動作します

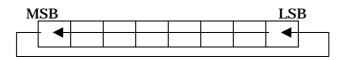

- ・RLF 命令: PIC16F84 では左シフト後の最下位ビットにはキャリーフラグの値が入りますが,本 IP では最下位ビットには最上位ビットの値が入ります.

図 2 RLF 命令の動き

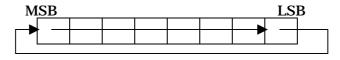

・RRF 命令: RLF 命令と同様に右シフト後の最上位ビットには, 最下位ビットの値が入ります.

図3 RRF 命令の動き

RLF命令・RRF命令は,piccore.vの中ほどにある以下の記述のコメントアウトの行を変えることにより,PIC16F84と同等の動作にすることができます.

```

if (INST_RLF == 1'b1) begin

aluout_reg <= {aluinp1_reg[6:0],aluinp1_reg[7]};

// aluout_reg <= {aluinp1_reg[6:0],status_reg[0]};

end else if (INST_RRF == 1'b1) begin

aluout_reg <= {aluinp1_reg[0],aluinp1_reg[7:1]};

// aluout_reg <= {status_reg[0],aluinp1_reg[7:1]};

end</pre>

```

#### 3.2 レジスタファイル

最大で 5 1 2 バイトのレジスタファイルにアクセスできますが , そのうち 4 8 バイトは特殊レジスタアクセスのために使われるので , 汎用レジスタとしては最大 4 6 4 バイト使用することができます .

| File Addı | ress          | File Ac       | ddress | File Addr | ess           | File Ad       | ldress |

|-----------|---------------|---------------|--------|-----------|---------------|---------------|--------|

| 00h       | Indirect addr | Indirect addr | 80h    | 100h      | Indirect addr | Indirect addr | 180h   |

| 01h       | TMR0          | OPTION        | 81h    | 101h      | TMR0          | OPTION        | 181h   |

| 02h       | PCL           | PCL           | 82h    | 102h      | PCL           | PCL           | 182h   |

| 03h       | STATUS        | STATUS 83h    |        | 103h      | STATUS        | STATUS        | 183h   |

| 04h       | FSR           | FSR           | 84h    | 104h      | FSR           | FSR           | 184h   |

| 05h       | PORTA         | TRISA         | 85h    | 105h      | PORTA         | TRISA         | 185h   |

| 06h       | PORTB         | TRISB         | 86h    | 106h      | PORTB         | TRISB         | 186h   |

| 07h       |               |               | 87h    | 107h      |               |               | 187h   |

| 08h       |               |               | 88h    | 108h      |               |               | 188h   |

| 09h       |               |               | 89h    | 109h      |               |               | 189h   |

| 0Ah       | PCLATH        | PCLATH        | 8Ah    | 10Ah      | PCLATH        | PCLATH        | 18Ah   |

| 0Bh       | INTCON        | INTCON        | 8Bh    | 10Bh      | INTCON        | INTCON        | 18Bh   |

| 0Ch       | 汎用            | 汎用            | 8Ch    | 10Ch      | 汎用            | 汎用            | 18Ch   |

|           | レジスタ          | レジスタ          |        |           | レジスタ          | レジスタ          |        |

| 7Fh       | 116 バイト       | 116 バイト       | FFh    | 17Fh      | 116 バイト       | 116 バイト       | 1FFh   |

| Bank0     |               | Bank1         |        | •         | Bank2         | Bank3         | -      |

図4 レジスタファイル配置

レジスタファイルの大きさは, dataram.v 中の reg [7:0] ram\_reg [0:511]; の配列の値を変えることで決定できます.

特殊レジスタでは, STATUS と OPTION に変更があります.

- ・STATUS[4]: ウォッチドッグタイマが実装されていないので常に1となります

- ・OPTION[7]: PORTB プルアップ機能は実装されていないので常に1して下さい

- ・OPTION[5:4]: RA4 ピンからの入力は TMR 0 クロックソースとしては使えなくなって いるので,この 2 ビットの値によらずクロックソースは常に内部命令サイクルクロック になります

- ・OPTION[3]: 0 にすると TMR0 にプリスケーラーが割り当てられ,1 にすると TMR0 にプリスケーラーが割り当てられません

#### 3.3 プログラム ROM

PIC のアセンブラ MPLAB が出力する HEX ファイルより,論理合成可能な progrom.v を作成します.progrom.v の作成には,HEXtoVerilog.exe(ホームページからダウンロードしてください)を使って行ってください.HEXtoVerilog.exe をダブルクリックすると,HEXファイル名と Verilog ファイル名を聞かれますのでそれぞれ入力してください.サンプルプログラムとして,PORTBにつなげた8つの LED が点滅するプログラムの HEX ファイルとprogrom.v を用意しました.ホームページよりダウンロードして使ってください. MPLAB は <a href="http://www.microchip.co.jp/">http://www.microchip.co.jp/</a>で入手することができます. <a href="http://www.microchip.co.jp/">HEX ファイルのフォーマットはINHX8Mを選択してください(各 project の Build Options...で変更できます.)外付けの flash メモリなどを用いる場合は,progrom.vをはずして合成してください.

#### 3.4 タイマ0

3.2節でも述べたように,タイマ0のクロックソースとして RA4 ピンからの入力は使用できません.よって,タイマ0のクロックソースとしては内部命令サイクルクロックのみになっています.

#### 3.5 スリープ

スリープ中は外部からのクロック供給を止めてやる必要があります.powerdown 信号は SLEEP 命令が実行されると high になります powerdown が high の間は ,クロックを high または low に保つようにして下さい. スリープ中に割り込みが入ったりリセットがかかったりすると,スリープ解除信号 startclkin が high になります.startclkin が high になったらクロック供給を再開してください.

### 4.本 IP の性能と今後の展望

ここでは,本 IP の動作周波数や消費電力,面積などの性能と今後の展望などを述べます.

#### 4 . 1 ROHM0.35 µ m での性能

・最高動作周波数:約140MHz

・消費電流:動作時 45mA @50MHz,3.3V (I/O は含まない)

待機時 2 µ A 以下@3.3V

・面積:4.9mm 角チップの約4分の1

ゲート数は 2NAND 換算で約3万ゲート

プログラム ROM は外付けとし,データメモリは256 バイトとした場合

#### 4 . 2 FPGA での性能

評価した FPGA は, xilinx の Spartan- XC2S150 です.

・最高動作周波数:約40MHz

・ゲート数:43000 ゲート

プログラム ROM はサンプルプログラムとし,データメモリは512 バイトとした場合

#### 4.3 今後の展望

プログラム ROM として外付けの flash を用いたり ,プログラムを合成したりするのはかなり使い勝手が悪いので , 改良版を考えています . 方式としては , プログラムメモリはレジスタファイルとしてチップの中に入れます . 実際のプログラムは外付けの EEPROM に書き込んでおき , コントローラの起動時に EEPROM より読み込むというものです . 完成したら VDEC にて公開いたします .

## 5 . 参考文献

電子工作のための PIC 活用ガイドブック

著 後閑哲也 技術評論社